# **ft690V** 2W Mono Audio Power Amplifier Datasheet (Rev. 1.0)

## Introductions

The ft690V is a mono Bridge-Tied Load (BTL) amplifier designed for handheld multimedia devices. When supplied with 5V voltage, the ft690V can deliver 1.25W power to an 8 $\Omega$  BTL load or 2W to a 4 $\Omega$  speaker with the THD+N rate lower than 1.0%. The ft690V requires few external component and features power saving shutdown mode which suit best for battery-supplied mobile devices.

# Features

- Power saving shutdown mode (customer configurable)

- Unity-gain stable

- Pop and click circuitry to eliminate noise during system power-on and shutdown

- Few external components required

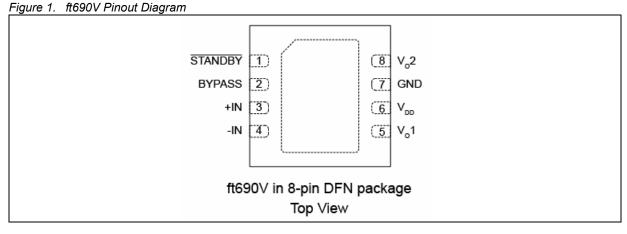

- Packages: 8-lead DFN package (3mm x 3mm)

# **Specifications**

- P<sub>0</sub> @ 1% THD+N, V<sub>DD</sub> = 5V

- R<sub>L</sub> = 4 $\Omega$ , P<sub>O</sub> = 2W (TYP)

- R<sub>L</sub> = 8Ω, P<sub>O</sub> = 1.25W (TYP)

- P<sub>0</sub> @ 1% THD+N, V<sub>DD</sub> = 3V

- R<sub>L</sub> = 4 $\Omega$ , P<sub>O</sub> = 600mW (TYP)

- $R_L = 8\Omega, P_O = 425 mW (TYP)$

- Shutdown current: 0.1µA

- Supply voltage range: 2.2 ~ 5.5V

- PSRR @ 217Hz and 1kHz: 66dB (TYP)

# **Packaging Details**

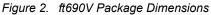

### ft690V

# **Application Information**

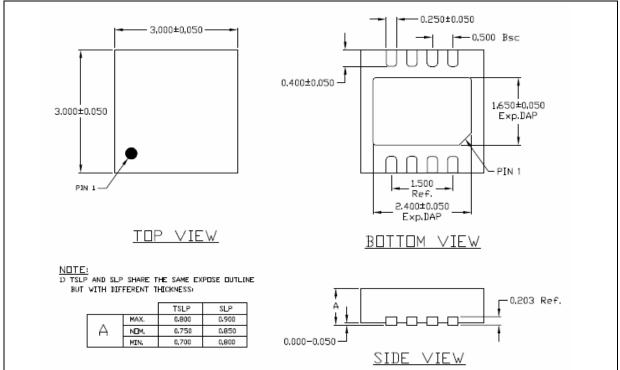

A single ft690V chip can be used to drive (1) one  $8\Omega$  speaker, or (2) one  $4\Omega$  speaker, or (3) two parallel-connected  $8\Omega$  speakers. Refer to Figure 3 below for application (1) or to 0 for applications (2) and (3).

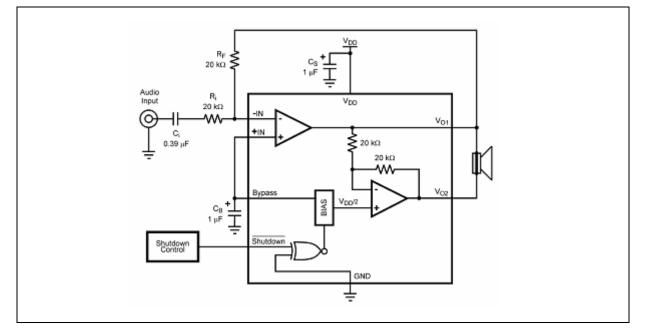

### Single 8Ω Speaker Output

The figure below shows the typical application circuitry using one single  $8\Omega$  speaker.

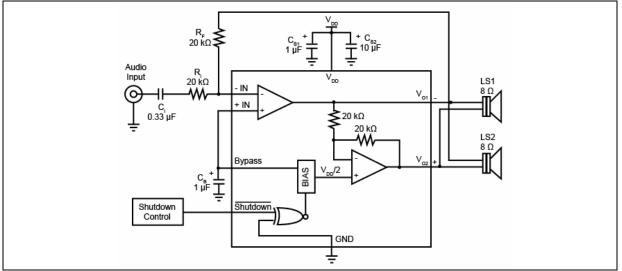

#### Single 4Ω Speaker or Dual Parallel-Connected 8Ω Speakers Output

The ft690V can be used to drive two parallel-connected  $8\Omega$  speakers to achieve greater output power. However, since the operation current sees greater variation under such working condition, an Equivalent Serial Resistor (ESR) capacitor of  $10\mu$ F or above is required at the chip supply end (V<sub>DD</sub>) to guarantee continuous supply and ensure the system stability. The circuitry routing is illustrated in Figure 4.

**Important:** When connecting the two 8Ω speakers in parallel, make sure that the phase positions of the two speakers are identical.

Figure 4. Dual 8Ω Parallel Connected Speakers/ Single 4Ω Speaker Application Circuitry

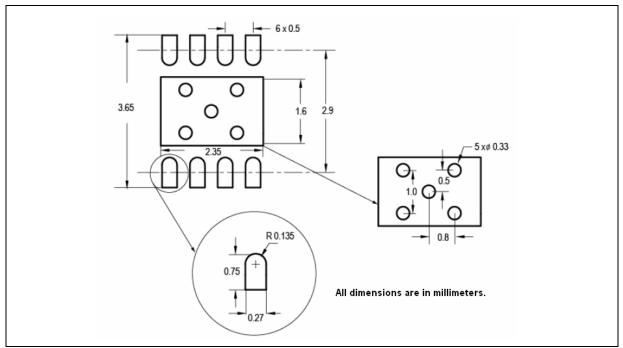

#### **Soldering Plate Design for Parallel Output**

The ft690V is packaged in 8-lead DFN with thermal pad at the bottom for connecting external heatsink. When the ft690V is applied to drive two parallel-connected  $8\Omega$  speakers, the operating current increases at a large scale which causes more power and heat dissipation. When the temperature exceeds the maximum ratings, the ft690V will be forced to shutdown by internal overheat protection circuitry. Therefore, heatsink issue should be taken into consideration when designing the printed circuit board (PCB).

When the thermal pad is soldered directly to the PCB board, the board acts like a heatsink to induct heat from the chip. In normal practice, through holes are often drilled in the soldering plate so as to induct heat to the inner layers or the bottom layer of the PCB to further enhance the heat induction. If through holes can not apply on the PCB, the copper-covered soldering plate area on which the thermal pad is soldered should be increased. Refer to Figure 5 below for the soldering plate dimensions and the through hole positions.

### **Bridged Amplifier**

The ft690V consists of two internal operational amplifiers to connect a speaker in BTL mode. The first amplifier receives signal input from the audio source and its gain is determined by two external resistors,  $R_I$  and  $R_F$ . The output from the first amplifier connects to the external speaker through the pin  $V_01$  while at the same time feeds into the second amplifier as signal input. The second amplifier, connecting to the speaker through pin  $V_02$ , provides a fixed gain of 1 by two internal 20k $\Omega$  resistors. The two outputs are identical in magnitude but opposite in phase which doubles the voltage gain of a single-end output. Refer to Figure 3 for circuitry reference.

The BTL mode amplifier provides up to four times the output power of that from a single-ended amplifier under the same condition. However, the power increase calculation assumes that the amplifier is not current limited or that the output signal is not clipped. Therefore, to ensure minimum output signal clipping, care must be taken when choosing the close-loop gain for the amplifier.

#### **Power Dissipation**

Power dissipation is critical for either single-ended or bridged amplifier board design. Equation (1) indicates the maximum power dissipation for a single-ended amplifier operating at a given supply voltage and driving a specified output load.

$P_{DMAX} = (V_{DD})^2 / (2\pi^2 R_L)$  Single-ended (1)

For ft690V where two operational amplifiers are included in a single package, the internal power dissipation is four times that of a single-ended amplifier, as indicated in Equation (2).

$$P_{DMAX} = 4 * (V_{DD})^2 / (2\pi^2 R_L)$$

Bridge mode (2)

Internal power dissipation is a function of output power and is directly related to  $P_{DMAX}$ , refer to Equation (3) below. The  $T_{JMAX}$  of the ft690V is 150°C. If the  $T_{JMAX}$  exceeds 150°C at a given output power, measures should be taken to reduce the thermal resistance to achieve higher  $T_{JMAX}$ , or to reduce supply voltage, increase load impedance, and/or reduce ambient temperature.

$P_{DMAX}' = (T_{JMAX} - T_A) / \Theta_{JA}$ (3)

#### **Power Supply Bypassing**

Proper power supply bypassing is essential for low noise performance and high power supply rejection in a power amplifier. The bypass capacitor ( $C_B$ ) should be placed as close to the device as possible to ensure the supply stability. However, the presence of  $C_B$  does not eliminate the need for a  $1.0\mu$ F tantalum bypass capacitor ( $C_S$ ) connected between the ft690V's power supply pins and the ground. Optimizing the length of leads and traces between the ft690V and ground also help to improve the power supply bypassing.

#### Shutdown Function

The ft690V's power saving scheme is realized through the SHUTDOWN pin. When the pin is pulled low, the shutdown mode is activated leaving a small idle current running across.

The shutdown can be initiated and controlled by either a single-pole, single-throw switch, or a microprocessor or microcontroller. When switch is employed to control the shutdown, an external resistor between the SHUTDOWN pin and the ground is needed. Closing the switch sets the amplifier in normal function, while opening the switch sets the SHUTDOWN pin to ground through the resistor and consequently activates the shutdown. The switch and resistor design guarantees that the SHUTDOWN pin is not float to prevent unwanted state changes. In digital systems, where microprocessors or microcontrollers are deployed, digital output can be applied to control the SHUTDOWN input voltage.

#### Components

Proper external components are essential for building up an ft690V system. Although the ft690V can function well with various external component combinations, the optimum performance and cost are achieved only with careful selection.

The ft690 is unity-gain stable which provides wide feasibility for system designers. The gain is set to meet individual application requirements but no higher in order to get minimum THD+N and maximum Signal-Noise Ratio (SNR). However, low gain demands input signals with greater voltage swings to achieve maximum output power. Fortunately, many signal sources such as CODECs have outputs of  $1V_{RMS}$ .

#### Input Capacitor

High value input coupling capacitors ( $C_1$ ) are required to amplifying the low inputting audio signal. However, high value capacitor can be expensive in cost and big in size which may become a fatal defect for handheld devices. Besides, the speakers in handheld and portable devices, either internal or external, seldom reproduce signals below 150Hz. Therefore, big input capacitor has very little influence in output signal quality in applications using limited frequency response speakers.

Besides the cost and size, the input capacitor also influences the click and pop performance. When the supply voltage is fed in, a transient (pop) is generated as the charge on the input capacitor changes from 0 to a quiescent state. The magnitude of the pop is proportional to the input capacitance. The higher the capacitance is, the more time it requires to reach quiescent DC voltage (usually 0.5V<sub>DD</sub>) when charged with a fixed current. The amplifier output charges the input capacitor through the feedback resistor. Therefore, pops can be minimized with input capacitance no higher than necessary.

#### **Bypass Capacitor**

Bypass capacitor determines the time needed for setting ft690V to quiescent operation and plays an important role in minimizing turn-on pops. The slower the output ramp to quiescent DC voltage ( $0.5V_{DD}$  nominal), the smaller the turn-on pop is. Bypass capacitor of 1µF is adopted in typical design.

# **Parametric Data**

### Absolute Maximum Ratings

*Caution!* The parameters provided in this table are the maximum values. Parameters exceeding these values may cause permanent damage to the device and the board.

| Parameters                                                | Value                     |

|-----------------------------------------------------------|---------------------------|

| Supply Voltage (V <sub>DD</sub> )                         | 6.0V                      |

| Storage Temperature (T <sub>STG</sub> )                   | -65 °C to +150 °C         |

| Input Voltage (V <sub>IN</sub> )                          | -0.3 V to $V_{DD}$ + 0.3V |

| Power Dissipation                                         | Internally Limited        |

| ESD Susceptibility                                        | 2000 V                    |

| Junction Temperature (T <sub>J</sub> )                    | 150 °C                    |

| Θ <sub>JC</sub> (MSOP)                                    | 56 °C/W                   |

| Θ <sub>JA</sub> (MSOP)                                    | 190 °C/W                  |

| Θ <sub>JC</sub> (WCSP)                                    | 180 °C/W                  |

| Θ <sub>JA</sub> (DFN)                                     | 63 °C/W                   |

| Θ <sub>JC</sub> (DFN)                                     | 12 °C/W                   |

| Lead temperature 1.6mm (1/16 in) from case for 10 seconds | 260 °C                    |

### **Recommended Operation Conditions**

| Item                                              | Condition                                          | Min. | Тур. | Max.                  | Unit |

|---------------------------------------------------|----------------------------------------------------|------|------|-----------------------|------|

| Supply Voltage (V <sub>DD</sub> )                 |                                                    | 2.5  |      | 5.5                   | V    |

| High-level input voltage ( $V_{IH}$ )             | SHUTDOWN                                           | 2    |      |                       | V    |

| Low-level input voltage (VIL)                     | SHUTDOWN                                           |      |      | 0.8                   | V    |

| Common-mode input voltage (V <sub>IC</sub> )      | $V_{\text{DD}}$ = 2.5 V, 5.5 V, CMRR $\leq$ -60 dB | 0.5  |      | V <sub>DD</sub> - 0.8 | V    |

| Operating free-air temperature, (T <sub>A</sub> ) |                                                    | -40  |      | 85                    | °C   |

| Load Impedance (Z <sub>L</sub> )                  |                                                    | 6.4  |      | 8                     | Ω    |

### **Electrical Characteristics**

**Note:** The following electrical characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. But note that specifications are not guaranteed for parameters where no limit is given. The typical value however, is a good indication of device performance.

All voltages in the following tables are specified at 25°C which is generally taken as parametric norm.

$V_{DD} = 5V, T_A = 25^{\circ}C$

| Symbol            | Parameter                         | Conditions                                                          | Min. | Тур.           | Max. | Unit |

|-------------------|-----------------------------------|---------------------------------------------------------------------|------|----------------|------|------|

| I <sub>DD</sub>   | Quiescent Power Supply Current    | $V_{IN}$ = 0 V, $I_{O}$ = 0 A, No load                              |      | 2.5            | 7    | mA   |

| 00                |                                   | $V_{IN}$ = 0 V, $I_{O}$ = 0 A, 8 $\Omega$ load                      |      | 3              | 10   |      |

| I <sub>SD</sub>   | Shutdown Current                  |                                                                     |      | 0.1            | 2.0  | μA   |

| V <sub>SDIH</sub> | Shutdown Voltage Input High       |                                                                     |      | 1.5            |      | V    |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low        |                                                                     |      | 1.3            |      | V    |

| Vos               | Output Offset Voltage             |                                                                     |      | 7              | 50   | mV   |

| R <sub>out</sub>  | Resistor Output to GND            |                                                                     | 7.0  | 8.5            | 9.7  | kΩ   |

| Po                | Output Power (8Ω)                 | THD+N = 1% (max);<br>f = 1kHz                                       | 0.9  | 1.25           |      | W    |

| 10                | Output Power (4Ω)                 |                                                                     |      | 2              |      | W    |

| T <sub>wu</sub>   | Wake-up time                      |                                                                     |      | 130            |      | ms   |

| THD+N             | Total Harmonic Distortion + Noise | P <sub>o</sub> = 0.5 Wrms; f = 1 kHz                                |      | 0.2            |      | %    |

| PSRR              | Power Supply Rejection Ratio      | $V_{ripple}$ = 200 mV sine p-p<br>Input terminated with 10 $\Omega$ | 55   | 66 (f = 217Hz) |      | dB   |

|                   |                                   |                                                                     |      | 76 (f = 1kHz)  |      | GD   |

#### $V_{DD} = 3V, T_A = 25^{\circ}C$

| Symbol            | Parameter                         | Conditions                                                          | Min. | Тур.           | Max. | Unit |

|-------------------|-----------------------------------|---------------------------------------------------------------------|------|----------------|------|------|

| I <sub>DD</sub>   | Quiescent Power Supply Current    | $V_{IN}$ = 0 V, $I_O$ = 0 A, No load                                |      | 1.6            | 7    | mA   |

|                   |                                   | $V_{IN}$ = 0 V, $I_O$ = 0 A, 8 $\Omega$ load                        |      | 2              | 9    |      |

| I <sub>SD</sub>   | Shutdown Current                  |                                                                     |      | 0.1            | 2.0  | μA   |

| V <sub>SDIH</sub> | Shutdown Voltage Input High       |                                                                     |      | 1.1            |      | V    |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low        |                                                                     |      | 0.9            |      | V    |

| V <sub>os</sub>   | Output Offset Voltage             |                                                                     |      | 7              | 50   | mV   |

| R <sub>OUT</sub>  | Resistor Output to GND            |                                                                     | 7.0  | 8.5            | 9.7  | kΩ   |

| Po                | Output Power (8Ω)                 | THD+N = 1% (max);<br>f = 1kHz                                       |      | 425            |      | W    |

| 10                | Output Power (4Ω)                 |                                                                     |      | 600            |      | W    |

| T <sub>WU</sub>   | Wake-up time                      |                                                                     |      | 80             |      | ms   |

| THD+N             | Total Harmonic Distortion + Noise | P <sub>o</sub> = 0.5 Wrms; f = 1kHz                                 |      | 0.1            |      | %    |

| PSRR              | Power Supply Rejection Ratio      | $V_{ripple}$ = 200 mV sine p-p<br>Input terminated with 10 $\Omega$ | 55   | 66 (f = 217Hz) |      | dB   |

|                   |                                   |                                                                     |      | 76 (f = 1kHz)  |      |      |

### $V_{DD}$ = 2.6V, $T_A$ = 25°C

| Symbol            | Parameter                         | Conditions                                                          | Min. | Тур.           | Max. | Unit |

|-------------------|-----------------------------------|---------------------------------------------------------------------|------|----------------|------|------|

| I <sub>DD</sub>   | Quiescent Power Supply Current    | $V_{IN}$ = 0 V, $I_O$ = 0 A, No load                                |      | 1.5            |      | mA   |

| טטי               |                                   | $V_{\text{IN}}$ = 0 V, $I_{\text{O}}$ = 0 A, 8 $\Omega$ load        |      | 2              |      |      |

| I <sub>SD</sub>   | Shutdown Current                  |                                                                     |      | 0.1            |      | μA   |

| V <sub>SDIH</sub> | Shutdown Voltage Input High       |                                                                     |      | 1.0            |      | V    |

| V <sub>SDIL</sub> | Shutdown Voltage Input Low        |                                                                     |      | 0.9            |      | V    |

| Vos               | Output Offset Voltage             |                                                                     |      | 5              | 50   | mV   |

| R <sub>OUT</sub>  | Resistor Output to GND            |                                                                     | 7.0  | 8.5            | 9.7  | kΩ   |

| Po                | Output Power (8Ω)                 | THD+N = 1% (max);<br>f = 1 kHz                                      |      | 300            |      | W    |

| 10                | Output Power (4Ω)                 |                                                                     |      | 400            |      | W    |

| Twu               | Wake-up time                      |                                                                     |      | 70             |      | ms   |

| THD+N             | Total Harmonic Distortion + Noise | PO = 0.5 Wrms; f = 1 kHz                                            |      | 0.1            |      | %    |

| PSRR              | Power Supply Rejection Ratio      | $V_{ripple}$ = 200 mV sine p-p<br>Input terminated with 10 $\Omega$ | 55   | 66 (f = 217Hz) |      | dB   |

|                   |                                   |                                                                     |      | 76 (f = 1kHz)  |      | GD   |

# **Important Notice**

- 1. Disclaimer: The information in document is intended to help you evaluate this product. Fangtek, Inc. makes no warranty, either expressed or implied, as to the product information herein listed, and reserves the right to change or discontinue work on this product without notice.

- 2. LIFE SUPPORT POLICY: FANGTEK'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF FANGTEK INC.

As used herein

1) Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2) A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

- 3. FANGTEK ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATIONS OR IMPROPER USE OR OPERATION OF ITS PRODUCTS

- 4. FANGTEK MAKES NO WARRANTY OR REPRESENTATION THAT ITS PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM FANGTEK OR ANY THIRD PARTY, AND FANGTEK MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO ITS PRODUCTS. FANGTEK SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING PATENTS, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. THE INFORMATION IN THIS DOCUMENT IS MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF FANGTEK PRODUCTS. FANGTEK ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE DOCUMENT PRESENTED HEREIN. FANGTEK MAKES NO WARRANTY WITH RESPECT TO ITS PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

- 6. Trademarks: The company and product names in this document may be the trademarks or registered trademarks of their respective manufacturers. Fangtek is trademark of Fangtek Inc.

#### North America Contact 20823 Stevens Creek Blvd., Suite 200 Cuparting

Suite 300 Cupertino CA 95014, U.S.A. Tel: +1-408-996-1098 Fax: +1-408-996-0339 Website: <u>www.fangtek.com</u> Email: <u>info@fangtek.com</u>

### Asia Pacific Contact

N. 2/F., 2, Lane 690, Bibo Rd. Zhangjiang Hi-tech Park, Pudong Dist. Shanghai, P.R.China, 201203 Tel: +86-755-82814515 Fax: +86-755-82539865 Website: www.jiayida.net Email: Imk@jiayida.net